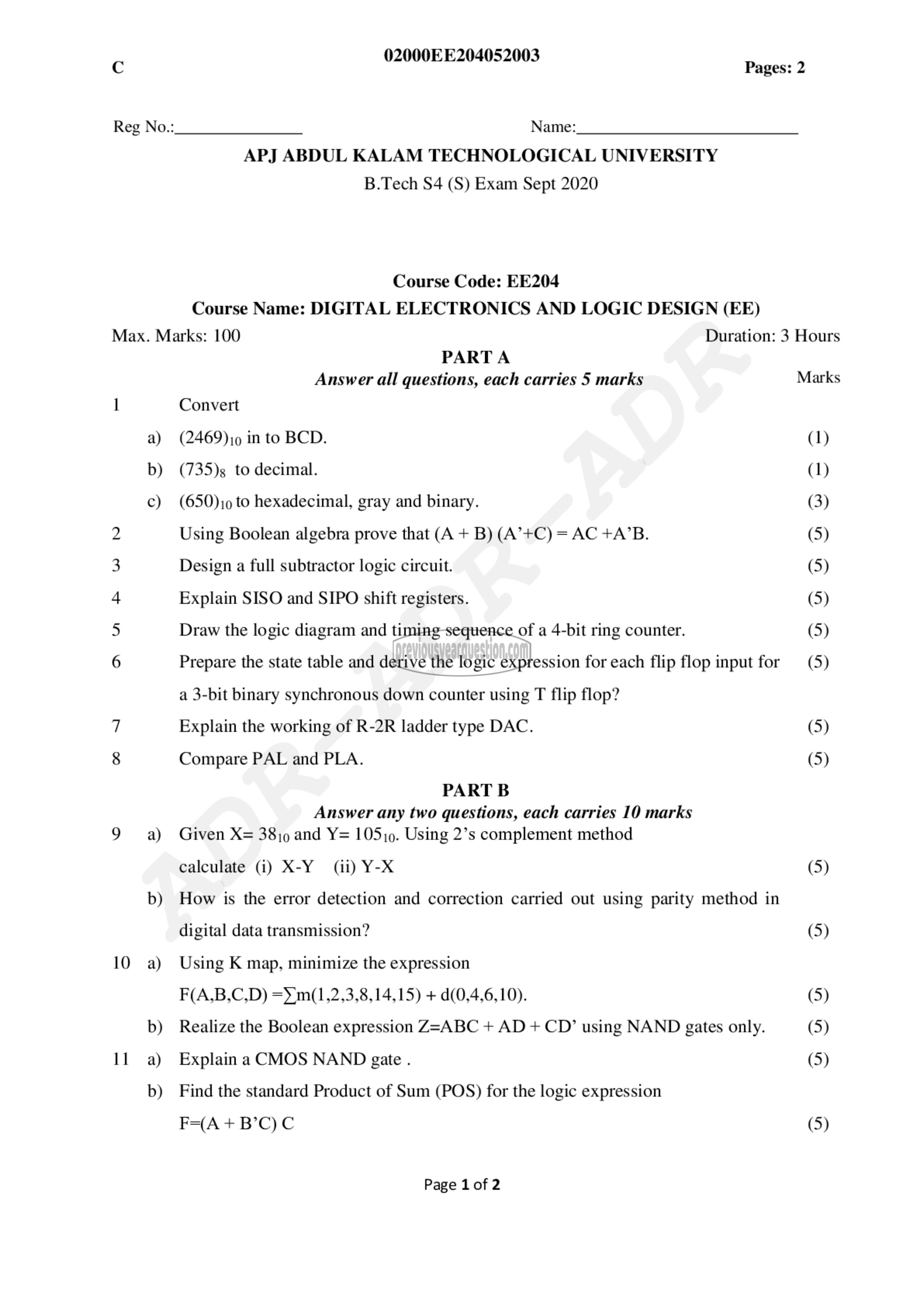

APJ ABDUL KALAM TECHNOLOGICAL UNIVERSITY Previous Years Question Paper & Answer

Semester : SEMESTER 4

Subject : Digital Electronics and Logic Design

Year : 2020

Term : SEPTEMBER

Scheme : 2015 Full Time

Course Code : EE 204

Page:1

Reg No.:

Max. Marks: 100

تم ~ طط ~ ರ

10

11

b)

௦)

a)

b)

02000EE204052003

Pages: 2

Name:

APJ ABDUL KALAM TECHNOLOGICAL UNIVERSITY

B.Tech S4 (S) Exam Sept 2020

Course Code: EE204

Course Name: DIGITAL ELECTRONICS AND LOGIC DESIGN (EE)

PARTA

Answer all questions, each carries 5 marks

Convert

(2469) in to BCD.

(735% to decimal.

(650010 hexadecimal, gray and binary.

Using Boolean algebra prove that (A + 3) (A’+C) = AC +A’B.

Design a full subtractor logic circuit.

Explain SISO and SIPO shift registers.

Draw the logic diagram and timing sequence of a 4-bit ring counter.

Prepare the state table and derive the logic expression for each flip flop input for

a 3-bit binary synchronous down counter using T flip flop?

Explain the working of R-2R ladder type DAC.

Compare PAL and PLA.

PART 13

Answer any two questions, each carries 10 marks

Given X= 3810 and Y= 10510. Using 2’s complement method

calculate (i) X-Y (ii) Y-X

How is the error detection and correction carried out using parity method in

digital data transmission?

Using K map, minimize the expression

F(A,B,C,D) 52 11(1,2,3,8,14, 15) + d(0,4,6,10).

Realize the Boolean expression Z=ABC + AD + CD’ using NAND gates only.

Explain a CMOS NAND gate .

Find the standard Product of Sum (POS) for the logic expression

F=(A + ٤07

Page 1 of 2

Duration: 3 Hours

Marks

(1)

(1)

(3)

(5)

(5)

(5)

(5)

(5)

(5)

(5)

(5)

(5)

(5)

(5)

(5)

(5)