APJ ABDUL KALAM TECHNOLOGICAL UNIVERSITY Previous Years Question Paper & Answer

Semester : SEMESTER 3

Subject : Logic Circuit Design

Year : 2020

Term : SEPTEMBER

Scheme : 2015 Full Time

Course Code : EC 207

Page:2

a)

b)

0)

a)

b)

00000EC207121904

Describe the working of a 3 bit TTL NAND gate in totem pole configuration. (8)

Convert a D flipflop into a JK flipflop, showing all the steps. (7)

PART C

Answer any two full questions, each carries 20 marks.

Explain the working of a 4 bit PISO register. Draw the circuit and timing diagram. (10)

Draw the Moore sequential model. How it differs from Mealy machine. (5)

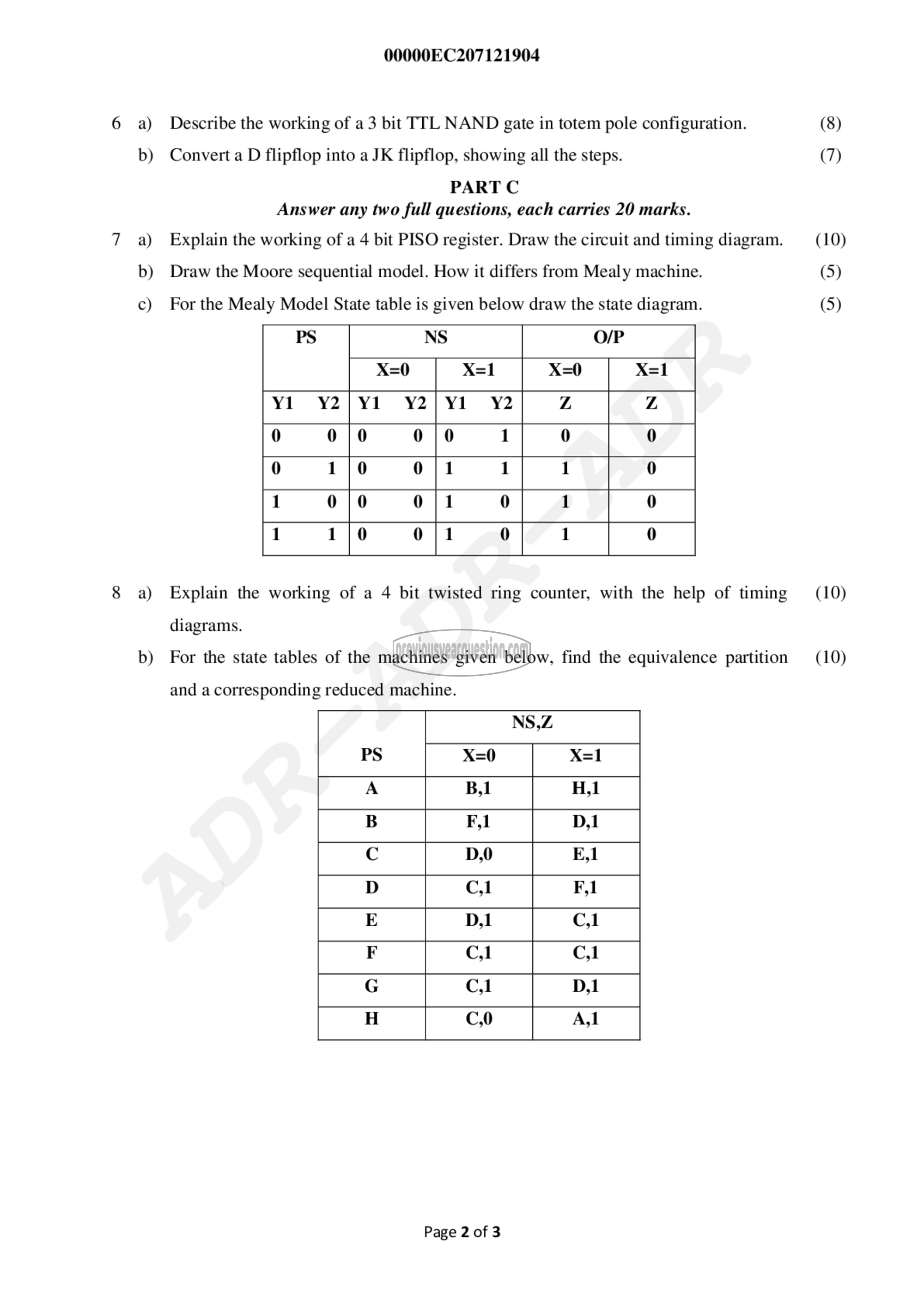

For the Mealy Model State table is given below draw the state diagram. (5)

Explain the working of a 4 bit twisted ring counter, with the help of timing (10)

diagrams.

For the state tables of the machines given below, find the equivalence partition (10)

and a corresponding reduced machine.

Page 2 of 3