APJ ABDUL KALAM TECHNOLOGICAL UNIVERSITY Previous Years Question Paper & Answer

Semester : SEMESTER 4

Subject : Digital Electronics and Logic Design

Year : 2019

Term : MAY

Scheme : 2015 Full Time

Course Code : EE 204

Page:1

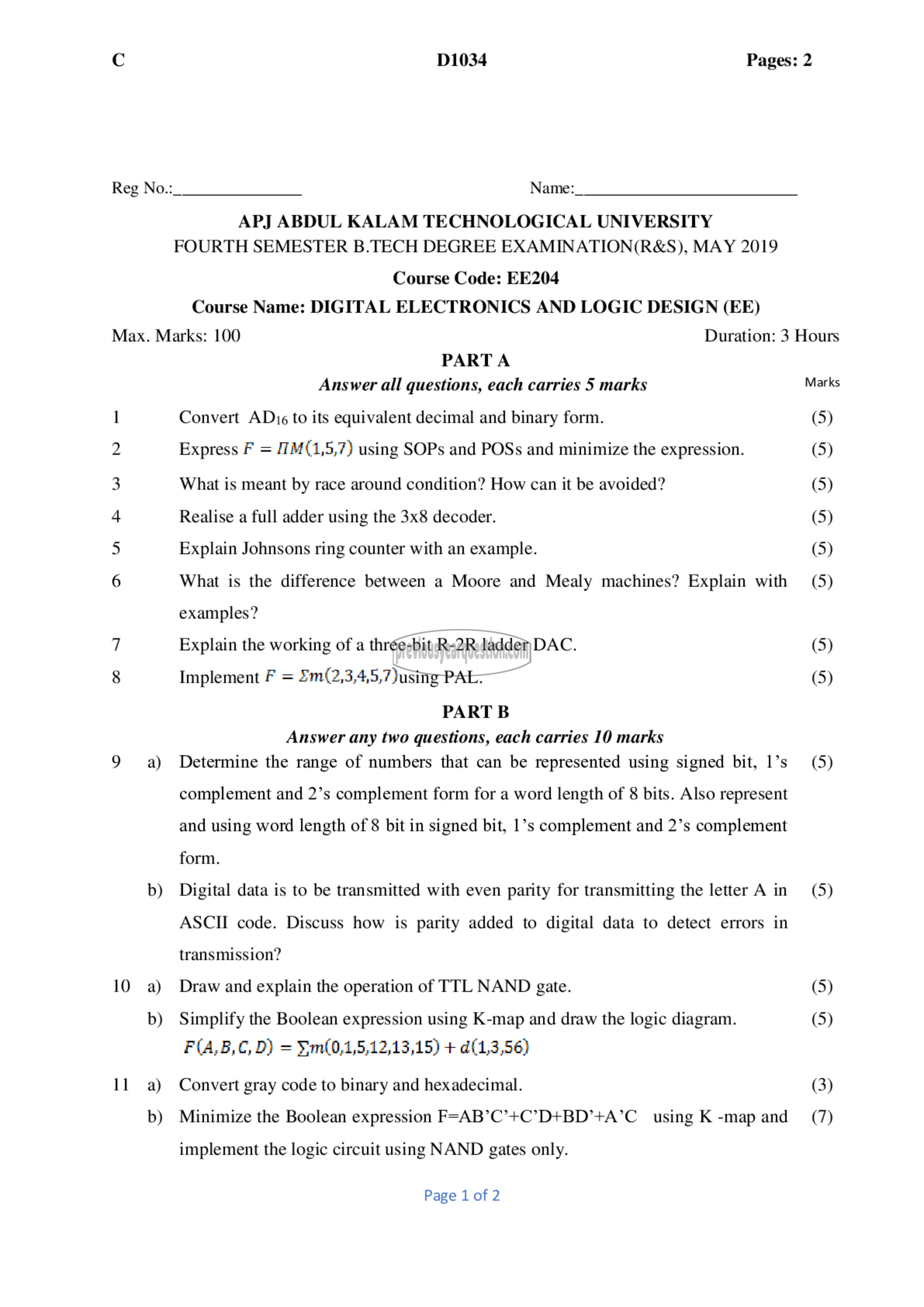

Cc D1034 Pages: 2

Reg No.:_ Name:

APJ ABDUL KALAM TECHNOLOGICAL UNIVERSITY

FOURTH SEMESTER B.TECH DEGREE EXAMINATION(R&S), MAY 2019

Course Code: EE204

Course Name: DIGITAL ELECTRONICS AND LOGIC DESIGN (EE)

Max. Marks: 100 Duration: 3 Hours

PARTA

Answer all questions, each carries 5 marks Marks

1 Convert ൧൧൦ to its equivalent decimal and binary form. (5)

2 Express F = 1111(1,5,7) using SOPs and POSs and minimize the expression. (5)

3 What is meant by race around condition? How can it be avoided? (5)

4 Realise a full adder using the 3x8 decoder. (5)

5 Explain Johnsons ring counter with an example. (5)

6 What is the difference between a Moore and Mealy machines? Explain with (5)

examples?

7 Explain the working of a three-bit R-2R ladder DAC. (5)

8 Implement F = Sm(2,3,4,5,7)using PAL. (5)

PART छ

Answer any two questions, each carries 10 marks

9 a) Determine the range of numbers that can be represented using signed bit, 15 (5)

complement and 2’s complement form for a word length of 8 bits. Also represent

and using word length of 8 bit in signed bit, 1’s complement and 2’s complement

form.

b) Digital data is to be transmitted with even parity for transmitting the letter A in (5)

ASCII code. Discuss how is parity added to digital data to detect errors in

transmission?

10 a) Draw and explain the operation of TTL NAND gate. (5)

b) Simplify the Boolean expression using K-map and draw the logic diagram. (5)

#7(4, 8, ८, 0) = ¥m(0,1,5,12,13,15) + 4(1,3,56)

11 a) Convert gray code to binary and hexadecimal. (3)

b) Minimize the Boolean expression F=AB’C’+C’D+BD’+A’C_ using K-map and _ (7)

implement the logic circuit using NAND gates only.

Page 1 of 2