APJ ABDUL KALAM TECHNOLOGICAL UNIVERSITY Previous Years Question Paper & Answer

Semester : SEMESTER 6

Subject : Comprehensive Exam

Year : 2019

Term : MAY

Scheme : 2015 Full Time

Course Code : EE 352

Page:3

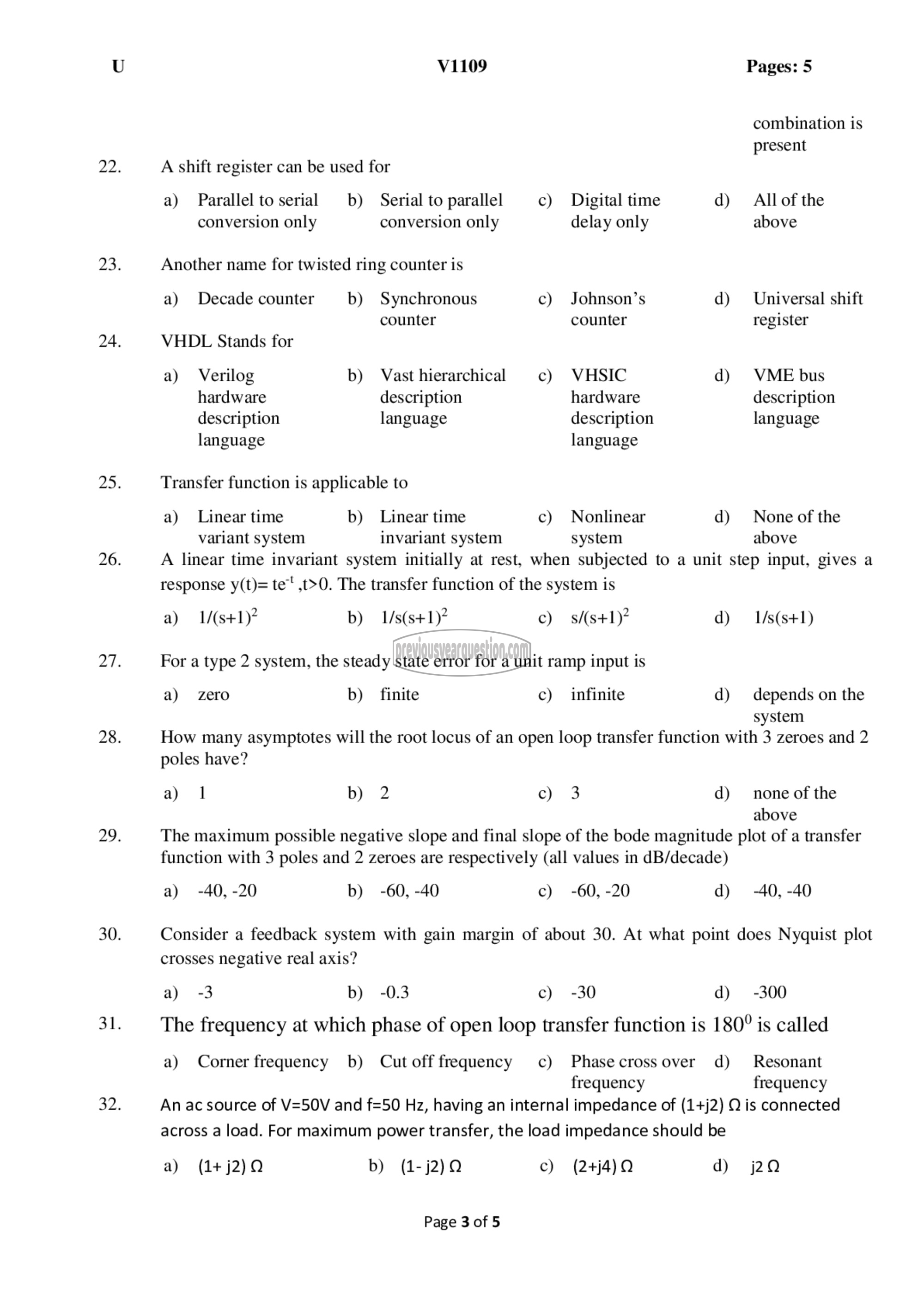

22.

23.

24.

23.

26.

27.

28.

29.

30.

31.

32.

V1109 Pages: 5

combination is

present

A shift register can be used for

a) Parallel to serial (ط Serial to parallel c) Digital time ५) Allof the

conversion only conversion only delay only above

Another name for twisted ring counter is

a) Decade counter b) Synchronous c) Johnson’s d) Universal shift

counter counter register

VHDL Stands for

a) Verilog b) Vast hierarchical c) VHSIC d) VME bus

hardware description hardware description

description language description language

language language

Transfer function is applicable to

a) Linear time b) Linear time c) Nonlinear d) None of the

variant system invariant system system above

A linear time invariant system initially at rest, when subjected to a unit step input, gives a

response y(t)= te‘ ,t>0O. The transfer function of the system is

a) 1(2+ع)/1 0) 1/5(5+ 1) ©) sKs+1)* 0) 1/5(8+1)

For a type 2 system, the steady state error for a unit ramp input is

a) zero b) finite c) infinite d) depends on the

system

How many asymptotes will the root locus of an open loop transfer function with 3 zeroes and 2

poles have?

a) 1 b) 2 c) 3 ५) none of the

above

The maximum possible negative slope and final slope of the bode magnitude plot of a transfer

function with 3 poles and 2 zeroes are respectively (all values in dB/decade)

a) -40, -20 0) -60, -40 ०) -60, -20 १) -40, -40

Consider a feedback system with gain margin of about 30. At what point does Nyquist plot

crosses negative real axis?

a) -3 0) -0.3 c) -30 0) -300

The frequency at which phase of open loop transfer function is 180° is called

a) Corner frequency رط Cutoff frequency ௦) Phasecrossover ம) Resonant

frequency frequency

An ac source of V=50V and f=50 Hz, having an internal impedance of (1+j2) ೧ is connected

across a load. For maximum power transfer, the load impedance should be

a) (1+ j2)Q 0) (1-12) 0 ௦) (2+4) 0 ५) 120

Page 3 of 5