APJ ABDUL KALAM TECHNOLOGICAL UNIVERSITY Previous Years Question Paper & Answer

Semester : SEMESTER 5

Subject : Digital System Design

Year : 2019

Term : DECEMBER

Scheme : 2015 Full Time

Course Code : EC 361

Page:3

a)

b)

a)

b)

a)

b)

a)

b)

01005 Pages:3

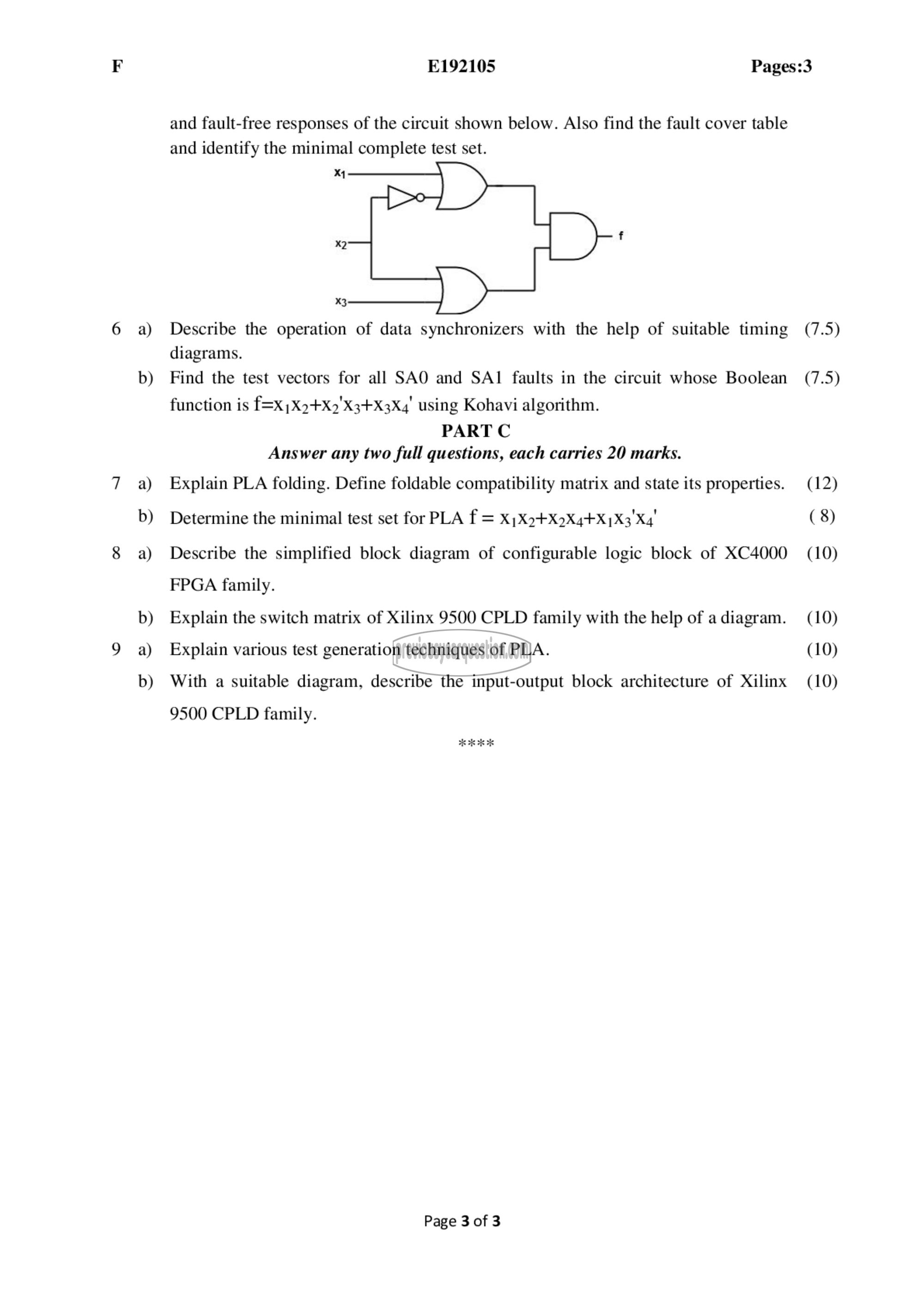

and fault-free responses of the circuit shown below. Also find the fault cover table

and identify the minimal complete test set.

೫1

೫2

x3

Describe the operation of data synchronizers with the help of suitable timing

diagrams.

Find the test vectors for all SAO and SAI faults in the circuit whose Boolean

function is f=x,X+X 'X3+X3X4' using Kohavi algorithm.

PART C

Answer any two full questions, each carries 20 marks.

Explain PLA folding. Define foldable compatibility matrix and state its properties.

Determine the minimal test set for PLA ரீ = X,X7+X2X4+X1X3'X4'

Describe the simplified block diagram of configurable logic block of XC4000

FPGA family.

Explain the switch matrix of Xilinx 9500 CPLD family with the help of a diagram.

Explain various test generation techniques of PLA.

With a suitable diagram, describe the input-output block architecture of Xilinx

9500 CPLD family.

Page 3 of 3

(7.5)

(7.5)

(12)

(8)

(10)

(10)

(10)

(10)