APJ ABDUL KALAM TECHNOLOGICAL UNIVERSITY Previous Years Question Paper & Answer

Semester : SEMESTER 1

Subject : Digital Control Systems

Year : 2015

Term : DECEMBER

Branch : CONTROL SYSTEMS

Scheme : 2015 Full Time

Course Code : 01 EE 6103

Page:2

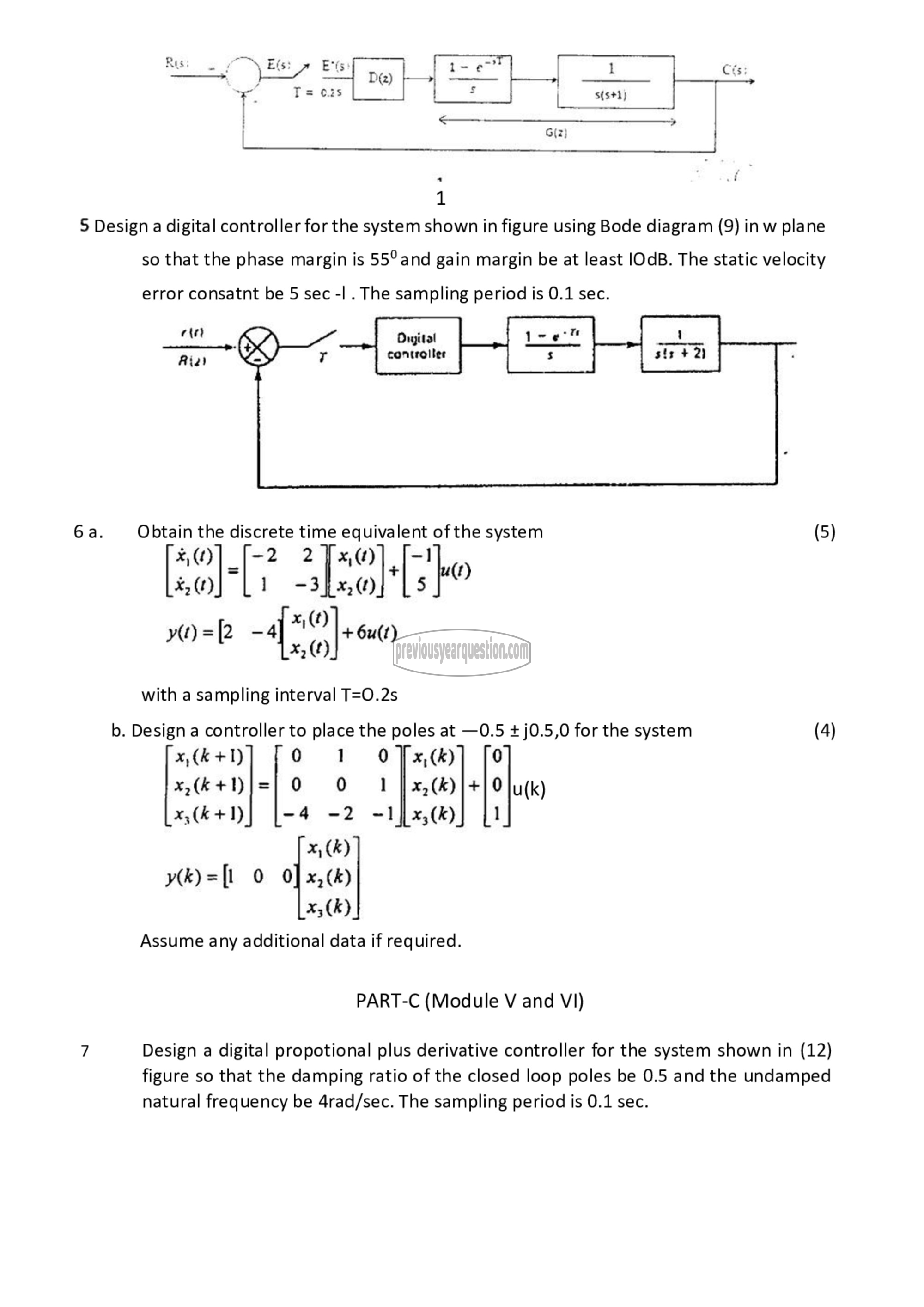

5 Design a digital controller for the system shown in figure using Bode diagram (9) in w plane

so that the phase margin is 55° and gain margin be at least 008. The static velocity

error consatnt be 5 sec ~| . The sampling period is 0.1 sec.

6a. Obtain the discrete time equivalent of the system

६, (४ -2 2 t -1

500] = 0] [-1], (6

x, (४) 1 531) 5

[ (1)

೫!) = [2 | (5640)

32 (४)

with a sampling interval 150.25

b. Design a controller to place the poles at —0.5 +j0.5,0 for the system

x,(k +1) 0 1 0 || ५) 0

(1050 0 1൧൧0൭0 u(k)

x,(k +1) -4 -2 -1|| x,(k) 1

x, £)

y(k)=[1 0 915൧

(8)

Assume any additional data if required.

PART-C (Module V and VI)

(5)

(4)

Design a digital propotional plus derivative controller for the system shown in (12)

figure so that the damping ratio of the closed loop poles be 0.5 and the undamped

natural frequency be 4rad/sec. The sampling period is 0.1 sec.