APJ ABDUL KALAM TECHNOLOGICAL UNIVERSITY Previous Years Question Paper & Answer

Semester : SEMESTER 2

Subject : Parallel Computer Architecture

Year : 2017

Term : MAY

Branch : COMPUTER SCIENCE AND ENGINEERING

Scheme : 2015 Full Time

Course Code : 01 CS 6102

Page:2

S. (a) Explain the different steps involved in hardware based specukation.

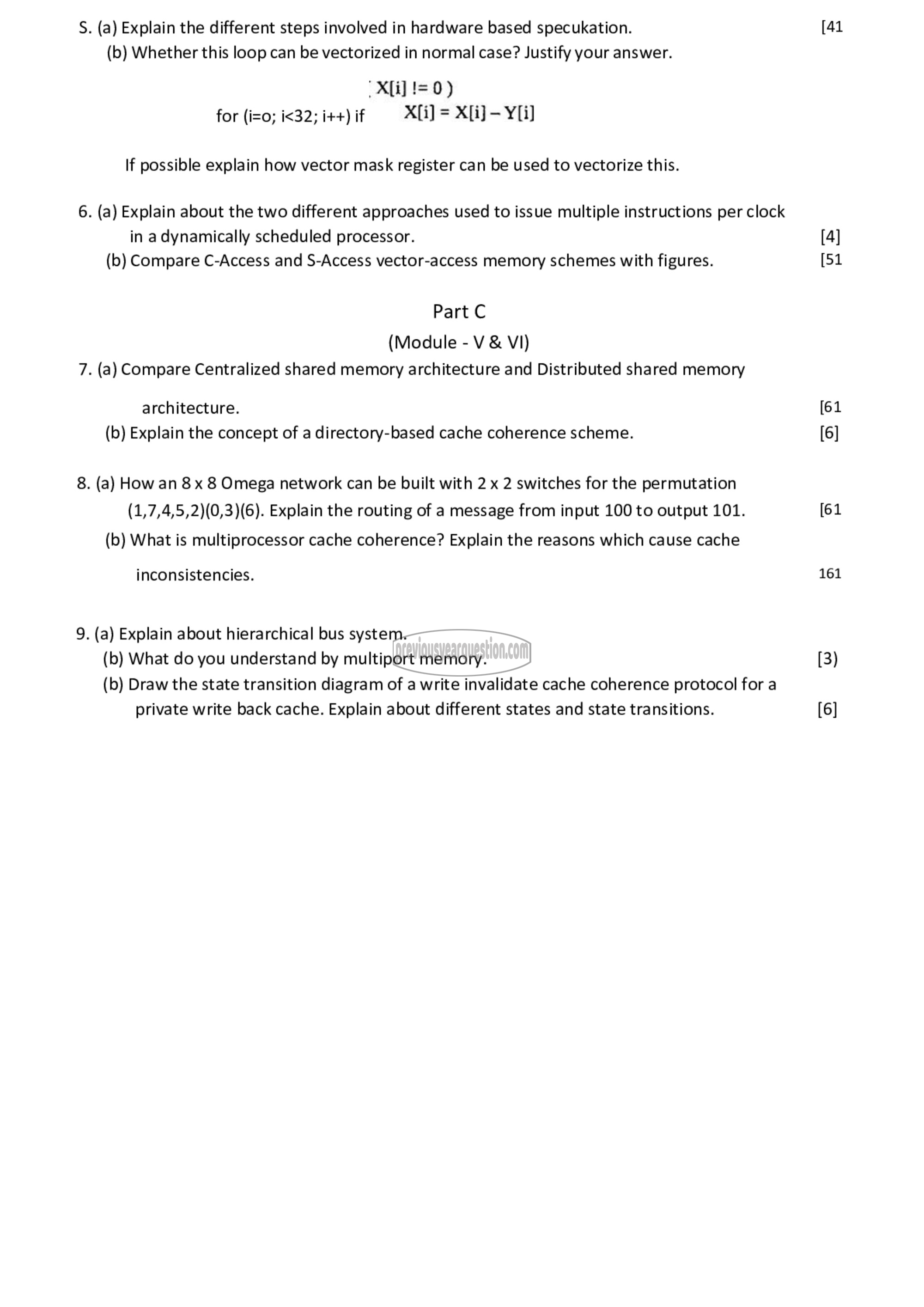

(b) Whether this loop can be vectorized in normal case? Justify your answer.

2001-0)

for (i=0; i<32; i++) if 201] = 20] - भा]

If possible explain how vector mask register can be used to vectorize this.

6. (a) Explain about the two different approaches used to issue multiple instructions per clock

in a dynamically scheduled processor.

(b) Compare C-Access and S-Access vector-access memory schemes with figures.

Part C

(Module - V & VI)

7. (a) Compare Centralized shared memory architecture and Distributed shared memory

architecture.

(b) Explain the concept of a directory-based cache coherence scheme.

8. (a) How an 8 x 8 Omega network can be built with 2 x 2 switches for the permutation

(1,7,4,5,2)(0,3)(6). Explain the routing of a message from input 100 to output 101.

(b) What is multiprocessor cache coherence? Explain the reasons which cause cache

inconsistencies.

9. (a) Explain about hierarchical bus system.

(b) What do you understand by multiport memory.

(b) Draw the state transition diagram of a write invalidate cache coherence protocol for a

private write back cache. Explain about different states and state transitions.

[41

[4]

[51

[61

[6]

[61

161

[3)

[6]