APJ ABDUL KALAM TECHNOLOGICAL UNIVERSITY Previous Years Question Paper & Answer

Semester : SEMESTER 1

Subject : DSP System Design

Year : 2015

Term : DECEMBER

Branch : SIGNAL PROCESSING

Scheme : 2015 Full Time

Course Code : 01 EC 6307

Page:1

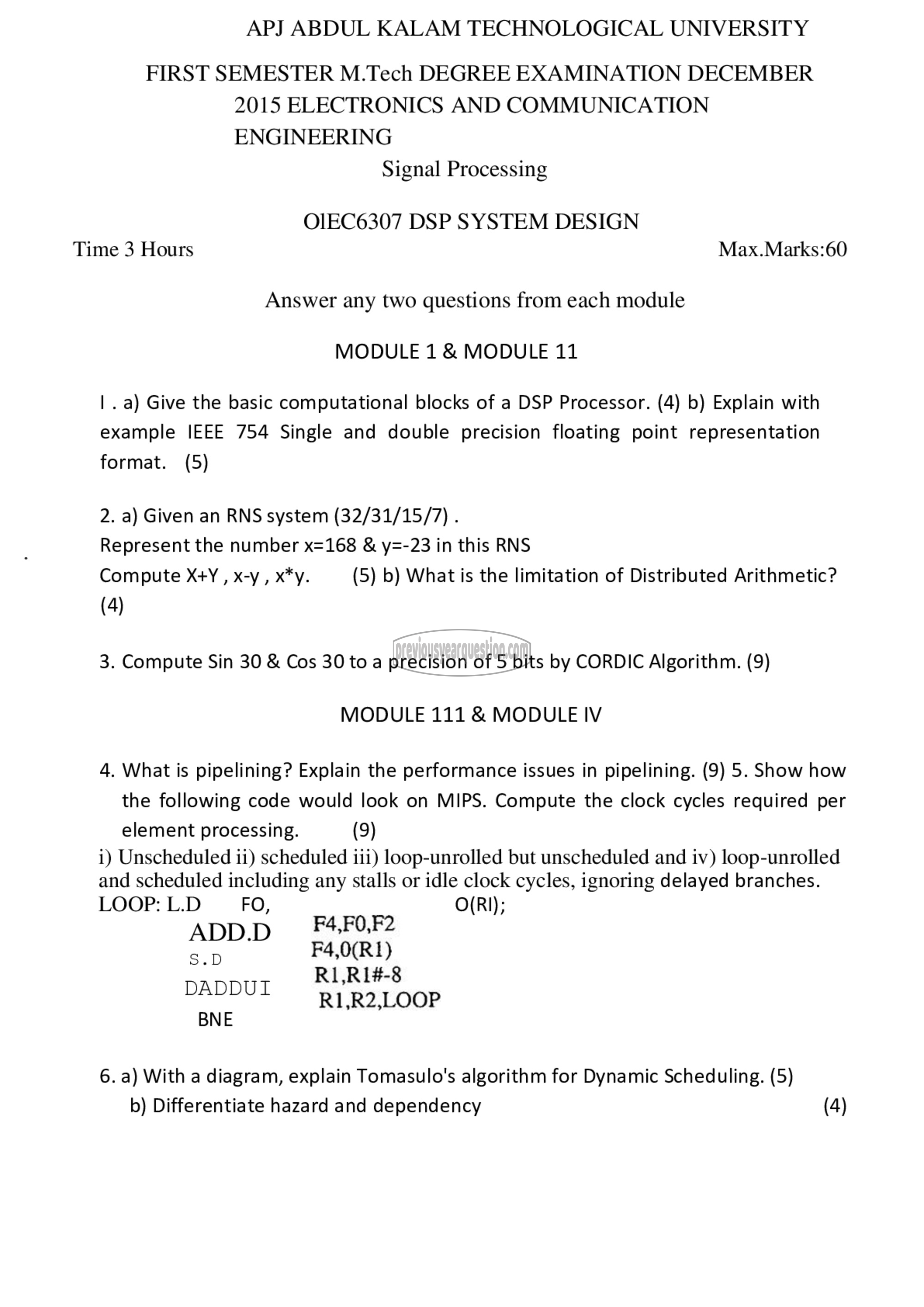

APJ ABDUL KALAM TECHNOLOGICAL UNIVERSITY

FIRST SEMESTER M.Tech DEGREE EXAMINATION DECEMBER

2015 ELECTRONICS AND COMMUNICATION

ENGINEERING

Signal Processing

OIEC6307 DSP SYSTEM DESIGN

Time 3 Hours Max.Marks:60

Answer any two questions from each module

MODULE 1 & MODULE 11

| . a) Give the basic computational blocks of a DSP Processor. (4) b) Explain with

example IEEE 754 Single and double precision floating point representation

format. (5)

2. a) Given an RNS system (32/31/15/7) .

Represent the number x=168 & y=-23 in this RNS

Compute X+Y , x-y, x*y. (5) b) What is the limitation of Distributed Arithmetic?

(4)

3. Compute Sin 30 & Cos 30 to a precision of 5 bits by CORDIC Algorithm. (9)

MODULE 111 & MODULE IV

4. What is pipelining? Explain the performance issues in pipelining. (9) 5. Show how

the following code would look on MIPS. Compute the clock cycles required per

element processing. (9)

i) Unscheduled 11) scheduled iii) loop-unrolled but unscheduled and iv) loop-unrolled

and scheduled including any stalls or idle clock cycles, ignoring delayed branches.

LOOP: L.D ₹0, O(RI);

ADD ೧ 848012

سد F4,0(R1)

RLRI#-8

DADDUI دنن ]دج 1م

BNE

6. a) With a diagram, explain Tomasulo's algorithm for Dynamic Scheduling. (5)

b) Differentiate hazard and dependency (4)