APJ ABDUL KALAM TECHNOLOGICAL UNIVERSITY Previous Years Question Paper & Answer

Semester : SEMESTER 6

Subject : Embedded System

Year : 2018

Term : MARCH

Scheme : 2015 Full Time

Course Code : EC 308

Page:83

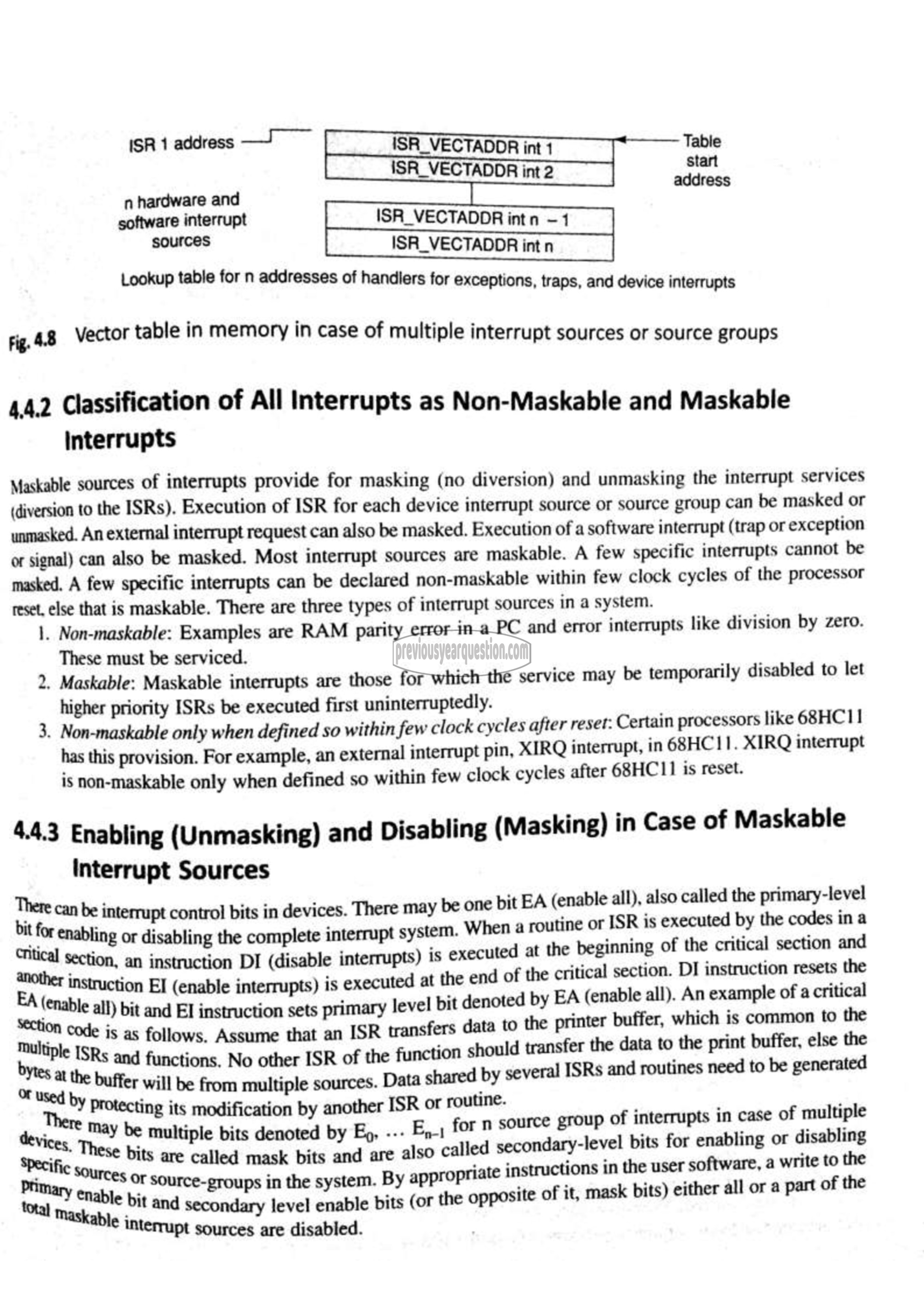

ISR 1 address — - ISR_VECTADDA int 1 ಹಾ

6 int 2 rel

address

n hardware and

software interrupt

sources

157. ४६01400१ int n - 1

ISR_VECTADDR int n

Lookup table for ೧ addresses of handlers for exceptions, traps, and device interrupts

fig. 4.8 Vector table in memory in case of multiple interrupt sources or source groups

44.2 Classification of All Interrupts as Non-Maskable and Maskable

Interrupts

Maskable sources of interrupts provide for masking (no diversion) and unmasking the interrupt services

(410108 to the ISRs). Execution of ISR for each device interrupt source or source group can be masked or

unmasked. An external interrupt request can also be masked. Execution of a software interrupt (trap or exception

or signal) can also be masked. Most interrupt sources are maskable. A few specific interrupts cannot be

masked. A few specific interrupts can be declared non-maskable within few clock cycles of the processor

reset, else that is maskable. There are three types of interrupt sources in a system.

|. Non-maskable: Examples are RAM parity error in a PC and error interrupts like division by zero.

These must be serviced.

2. Maskable: Maskable interrupts are those for which the service may be temporarily disabled to let

higher priority ISRs be executed first uninterruptedly.

3. Non-maskable only when defined so within few clock cycles after reset: Certain processors like 1

has this provision. For example, an external interrupt pin, XIRQ interrupt, in 68HC11. XIRQ interrupt

is non-maskable only when defined so within few clock cycles after 6811011 is reset.

4.4.3 Enabling (Unmasking) and Disabling (Masking) in Case of Maskable

Interrupt Sources

५४ can be interrupt control bits in devices. There may be

108 enabling or disabling the complete interrupt system.

೮70೦೫! section, an instruction DI (disable interrupts) 15 exec

another instruction EI (enable interrupts) is executed at the en

or 0

عاد Protecting its modification by another ISR or routine. 9

ಕೇಳ may be multiple bits denoted by Ep, -.. لمع for n source group of interrupts in case of multip le

ಅಷ್ಟ bits are called mask bits and are also called secondary-level bits for enabling or disabling

Pinan mess ण source-groups in the system. By appropriate instructions in the user software, a write om

tota} ₹7೩ bit and secondary level enable bits (or the opposite of it, mask bits) either all or a part ©

6 interrupt sources are disabled.