APJ ABDUL KALAM TECHNOLOGICAL UNIVERSITY Previous Years Question Paper & Answer

Semester : SEMESTER 6

Subject : Embedded System

Year : 2018

Term : MARCH

Scheme : 2015 Full Time

Course Code : EC 308

Page:82

An extemal device may also send to the processor the 151۷۲۳

Table 4.1). ۱ ಕ್

⋅ ⋅∙ ∙ service mechanism, Which associates a processor.

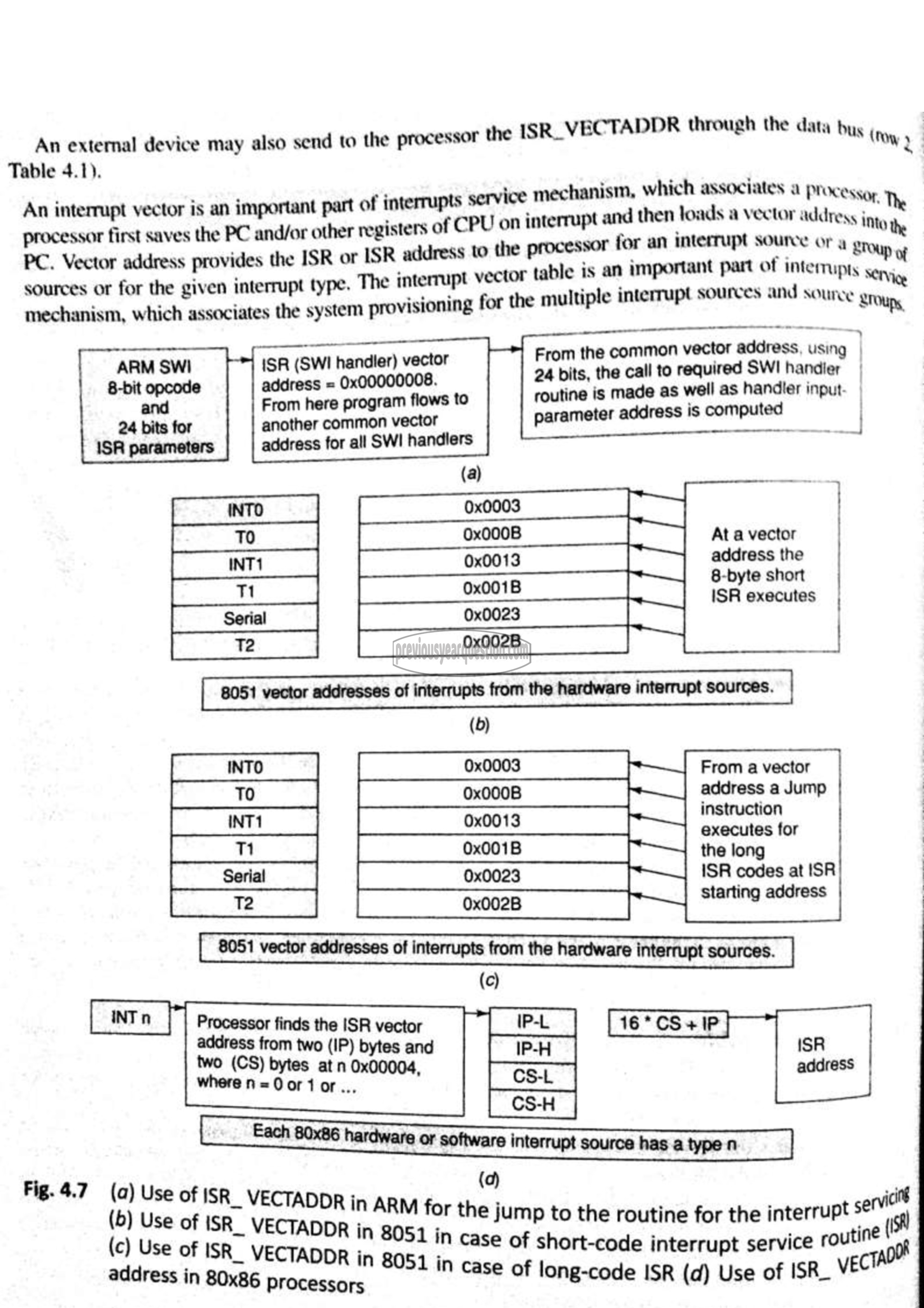

An interrupt vector is an important part of interrupts | ക

processor 0 saves the PC and/or other registers of CPU on interrupt and ಹ سمه avec بت वताता

PC. Vector address provides the ISR or ISR address to the processor for ടം की ദില;

sources or for the given interrupt type. The intermupt vector table is an 11110 [ സ്പ ബം

۱ 4 ் ⋅∙∙ iple i sources and source g

mechanism, which associates the system provisioning for the multiple interrupt sc Sand source 59

ADDR through the data bus (ஷே

3

ا ع

ಶ್ From the common vector address, using | ا

---------

ARM SWI 15೧ (SWI handler) vector ‘ red SWi hand

opcode 00000008 4 bits, the call to requ er

566 म flows ಸರತೆ is made as well as iri input. |

24 bits for another common vector parameter address 5ا 00 ja |

address for all SWI handlers

address the

8-byte short

ISR executes

From a vector

address a Jump

instruction

executes for |

the long |

ISR codes at ISR |

starting address |

Processor finds the ISR vector

address from two (IP) bytes and

two (CS) bytes at n 0x00004,

where n = 0 or 1 சொய்:

(०)

7

Rin ARM for the jump to the routine for the interrupt servic

Fig. 4.7 (0) Use of ISR_ VECTADD

address in 80x86 processors 051 in case of long-code ISR (d) Use of ISR_ ४