APJ ABDUL KALAM TECHNOLOGICAL UNIVERSITY Previous Years Question Paper & Answer

Semester : SEMESTER 6

Subject : Embedded System

Year : 2018

Term : MARCH

Scheme : 2015 Full Time

Course Code : EC 308

Page:17

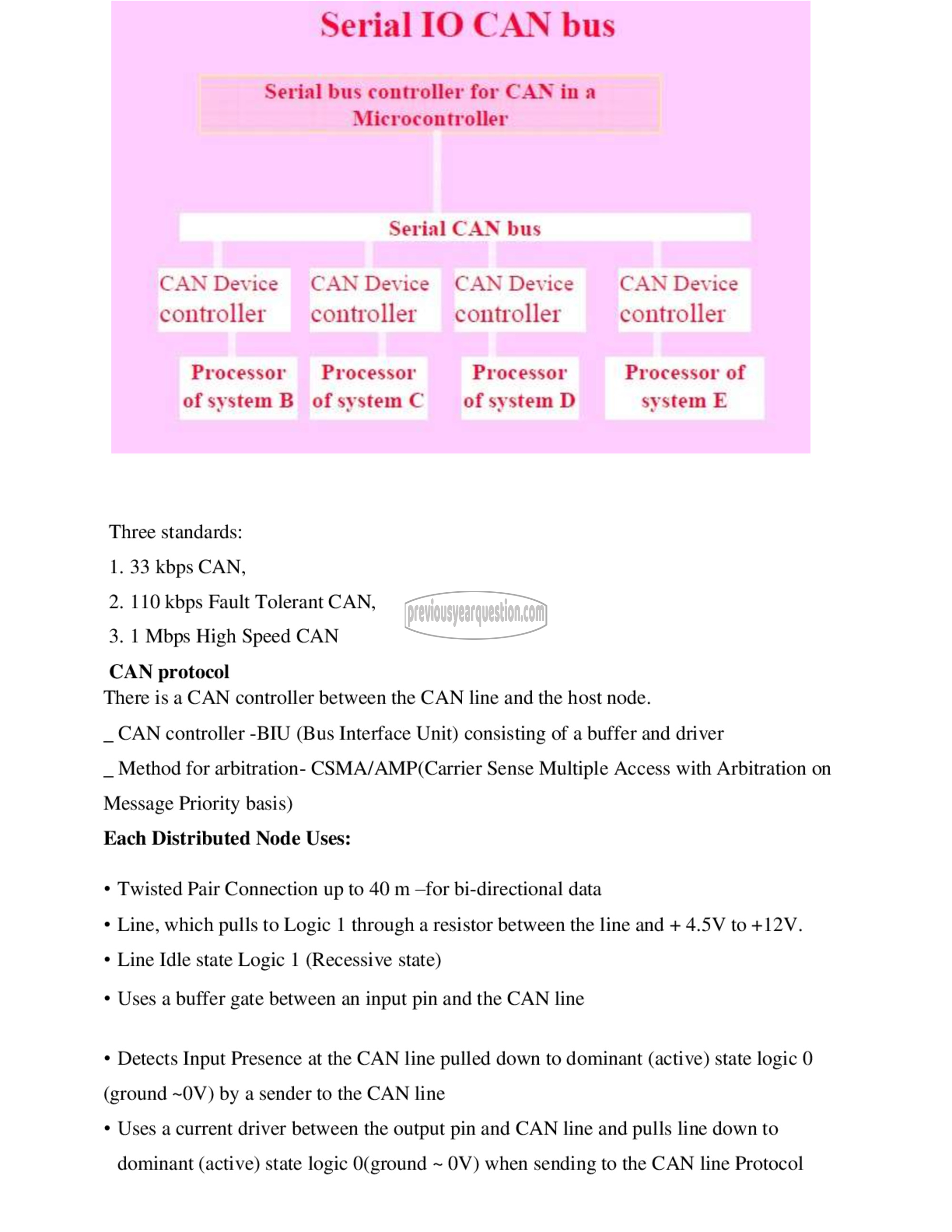

Serial 10 CAN bus

Serial bus controller for CAN ina

Microcontroller

Serial CAN bus

CAN Device CAN Device CAN Device CAN Device

controller controller controller controller

Processor Processor Processor Processor of

of system 8 of system ^ of system D system E

Three standards:

1. 33 kbps CAN,

2. 110 kbps Fault Tolerant CAN,

3. 1 Mbps High Speed CAN

CAN protocol

There is a CAN controller between the CAN line and the host node.

_ CAN controller -BIU (Bus Interface Unit) consisting of a buffer and driver

_ Method for arbitration- CSMA/AMP(Carrier Sense Multiple Access with Arbitration on

Message Priority basis)

Each Distributed Node Uses:

* Twisted Pair Connection up to 40 m —-for bi-directional data

* Line, which pulls to Logic 1 through a resistor between the line and + 4.5V to +12V.

* Line Idle state Logic 1 (Recessive state)

* Uses a buffer gate between an input pin and the CAN line

* Detects Input Presence at the CAN line pulled down to dominant (active) state logic 0

(ground ~OV) by a sender to the CAN line

* Uses a current driver between the output pin and CAN line and pulls line down to

dominant (active) state logic O(ground ~ 0५9) when sending to the CAN line Protocol