APJ ABDUL KALAM TECHNOLOGICAL UNIVERSITY Previous Years Question Paper & Answer

Semester : SEMESTER 6

Subject : Embedded System

Year : 2018

Term : MARCH

Scheme : 2015 Full Time

Course Code : EC 308

Page:15

A master device sends the sequence S ADDR W and then waits for an acknowledge

bit (A) from the slave which the slave will only generate if its internal address matches

the value sent by the master. If = this happens then the master sends DATA and waits

for acknowledge (A) from the slave. The master completes the byte tran sfer by generating

a stop bit (P) (or repeated start)

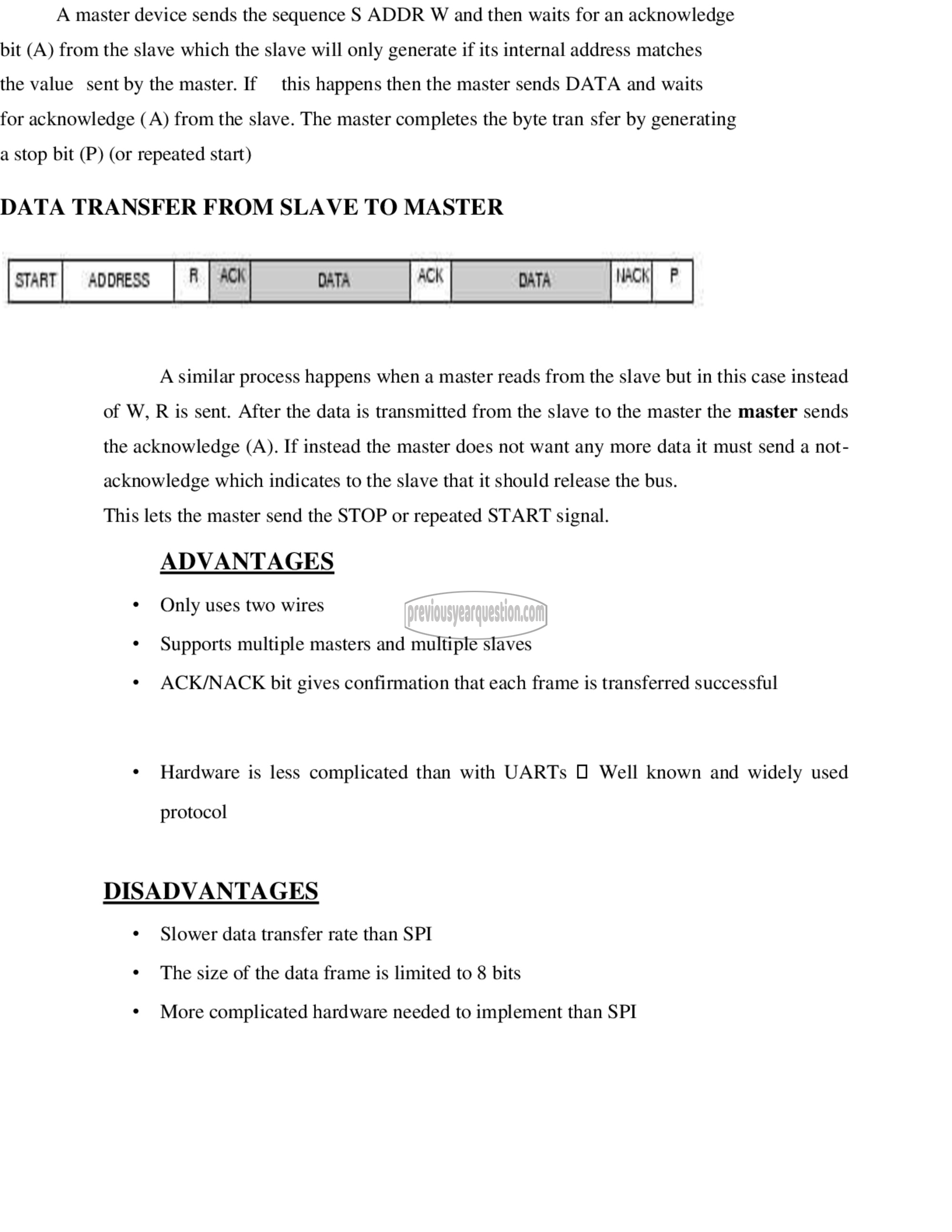

DATA TRANSFER FROM SLAVE TO MASTER

ADDRESS

A similar process happens when a master reads from the slave but in this case instead

of W, R is sent. After the data is transmitted from the slave to the master the master sends

the acknowledge (A). If instead the master does not want any more data it must send a not-

acknowledge which indicates to the slave that it should release the bus.

This lets the master send the STOP or repeated START signal.

ADVANTAGES

٠ Only uses two wires

٠ Supports multiple masters and multiple slaves

٠ ACK/NACK bit gives confirmation that each frame is transferred successful

Hardware is less complicated than with UARTs பி Well known and widely used ٭

protocol

DISADVANTAGES

٠ Slower data transfer rate than SPI

¢ The size of the data frame is limited to 8 bits

* More complicated hardware needed to implement than SPI