APJ ABDUL KALAM TECHNOLOGICAL UNIVERSITY Previous Years Question Paper & Answer

Semester : SEMESTER 3

Subject : Logic Circuit Design

Year : 2017

Term : JANUARY

Scheme : 2015 Full Time

Course Code : EC 207

Page:1

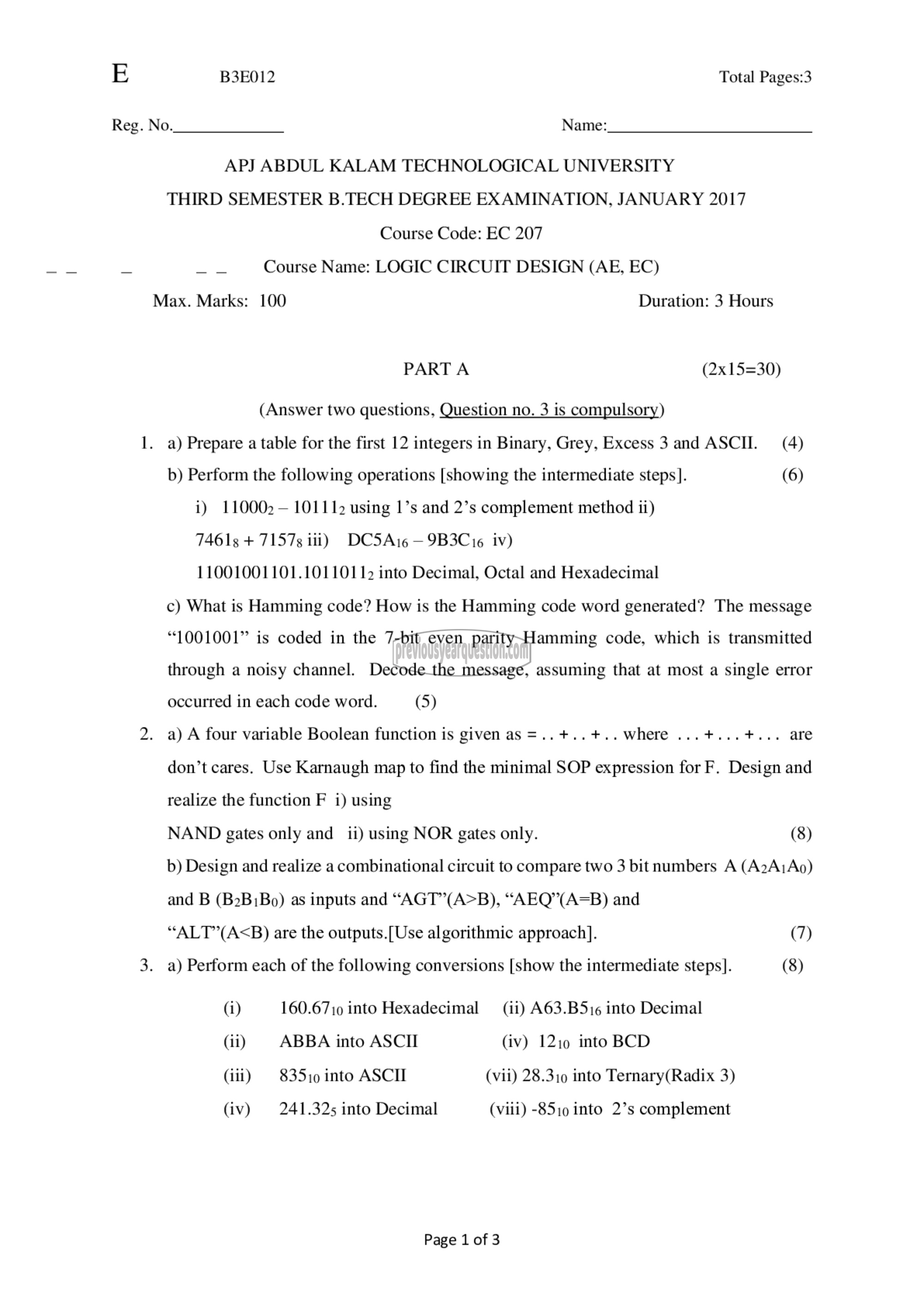

E B3E012 Total Pages:3

Reg. No. Name:

APJ ABDUL KALAM TECHNOLOGICAL UNIVERSITY

THIRD SEMESTER B.TECH DEGREE EXAMINATION, JANUARY 2017

Course Code: EC 207

−− − −− Course Name: LOGIC CIRCUIT DESIGN (AE, EC)

Max. Marks: 100 Duration: 3 Hours

PART A (2x15=30)

(Answer two questions, Question no. 3 is compulsory)

1. a) Prepare a table for the first 12 integers in Binary, Grey, Excess 3 and ASCII. (4)

b) Perform the following operations [showing the intermediate steps]. (6)

i) 110002 - 101112 using 1’s and 2’s complement method 11)

74618 + 7157s 111) 0054೬ — 9830016 iv)

11001001101.10110112 into Decimal, Octal and Hexadecimal

c) What is Hamming code? How is the Hamming code word generated? The message

“1001001” is coded in the 7-bit even parity Hamming code, which is transmitted

through a noisy channel. Decode the message, assuming that at most a single error

occurred in each code word. (5)

2. a) A four variable Boolean function is given as=..+..+.. Where ...+...+... are

don’t cares. Use Karnaugh map to find the minimal SOP expression for F. Design and

realize the function F i) using

NAND gates only வாம் ii) using NOR gates only. (8)

b) Design and realize a combinational circuit to compare two 3 bit numbers A (^ 24140)

and B (828180) as inputs and “AGT”’(A>B), “AEQ’(A=B) and

“ALT’(A

3. a) Perform each of the following conversions [show the intermediate steps]. (8)

(i) 160.6710 into Hexadecimal (01) A63.B516 into Decimal

(ii) ABBA into ASCII (iv) 12/0 into BCD

(111) 83510110 ASCII (vii) 28.310 into Ternary(Radix 3)

(iv) 241.325 into Decimal (viii) -8510 into 2’s complement

Page 1 of 3