APJ ABDUL KALAM TECHNOLOGICAL UNIVERSITY Previous Years Question Paper & Answer

Semester : SEMESTER 3

Subject : Analog Electronic Circuits

Year : 2018

Term : DECEMBER

Scheme : 2015 Full Time

Course Code : EE 203

Page:1

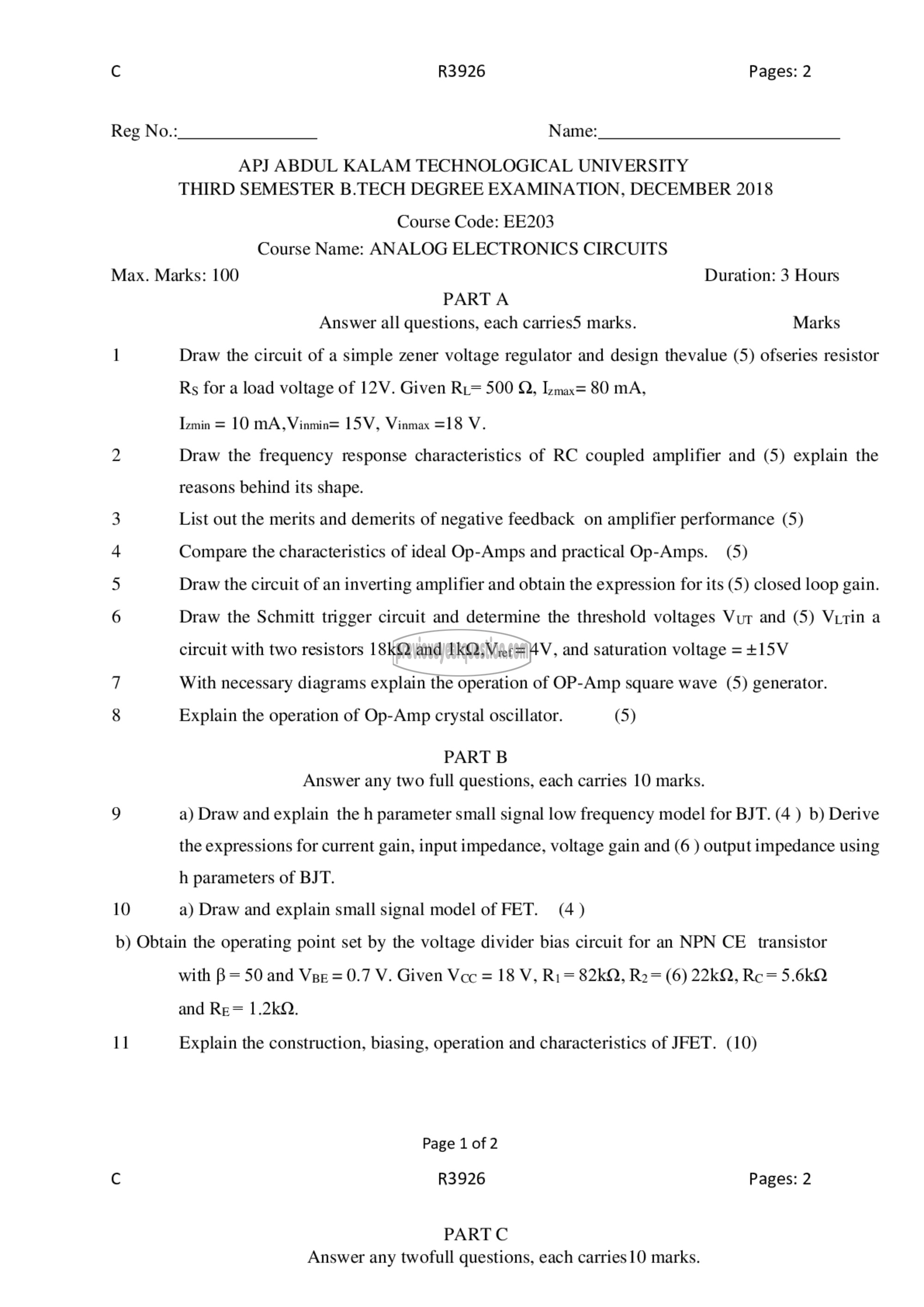

6 R3926 Pages: 2

Reg No.: Name:

APJ ABDUL KALAM TECHNOLOGICAL UNIVERSITY

THIRD SEMESTER B.TECH DEGREE EXAMINATION, DECEMBER 2018

Course Code: EE203

Course Name: ANALOG ELECTRONICS CIRCUITS

Max. Marks: 100 Duration: 3 Hours

PART A

Answer all questions, each carries5 marks. Marks

1 Draw the circuit of a simple zener voltage regulator and design thevalue (5) ofseries resistor

Rs for a load voltage of 12V. Given 1२5 500 Q, Izmax= 80 mA,

[णण = 10 mA, Vinmin= 15%, Vinmax =18 V.

2 Draw the frequency response characteristics of RC coupled amplifier and (5) explain the

reasons behind its shape.

3 List out the merits and demerits of negative feedback on amplifier performance (5)

4 Compare the characteristics of ideal Op-Amps and practical Op-Amps. (5)

5 Draw the circuit of an inverting amplifier and obtain the expression for its (5) closed loop gain.

6 Draw the Schmitt trigger circuit and determine the threshold voltages Vur and (5) ص۷ a

circuit with two resistors 18kQ and 1kQ,Vrer=4V, and saturation voltage = +15V

7 With necessary diagrams explain the operation of OP-Amp square wave (5) generator.

8 Explain the operation of Op-Amp crystal oscillator. (5)

PART B

Answer any two full questions, each carries 10 marks.

9 a) Draw and explain the h parameter small signal low frequency model for BJT. (4) b) Derive

the expressions for current gain, input impedance, voltage gain and (6 ) output impedance using

h parameters of BJT.

10 a) Draw and explain small signal model of FET. (2)

b) Obtain the operating point set by the voltage divider bias circuit for an NPN CE transistor

with B = 50 and ४४६ = 0.7۷۰ Given Vcc = 18 ५, Ri = 821८2, 1२2८ (6) 22kQ, २८ = 5.600

and रए = 1.2kQ.

11 Explain the construction, biasing, operation and characteristics of JFET. (10)

Page 1 of 2

€ ௩3926 Pages: 2

PARTC

Answer any twofull questions, each carries 10 marks.