APJ ABDUL KALAM TECHNOLOGICAL UNIVERSITY Previous Years Question Paper & Answer

Semester : SEMESTER 4

Subject : Digital Electronics and Logic Design

Year : 2018

Term : DECEMBER

Scheme : 2015 Full Time

Course Code : EE 204

Page:2

$2067 Pages; 2

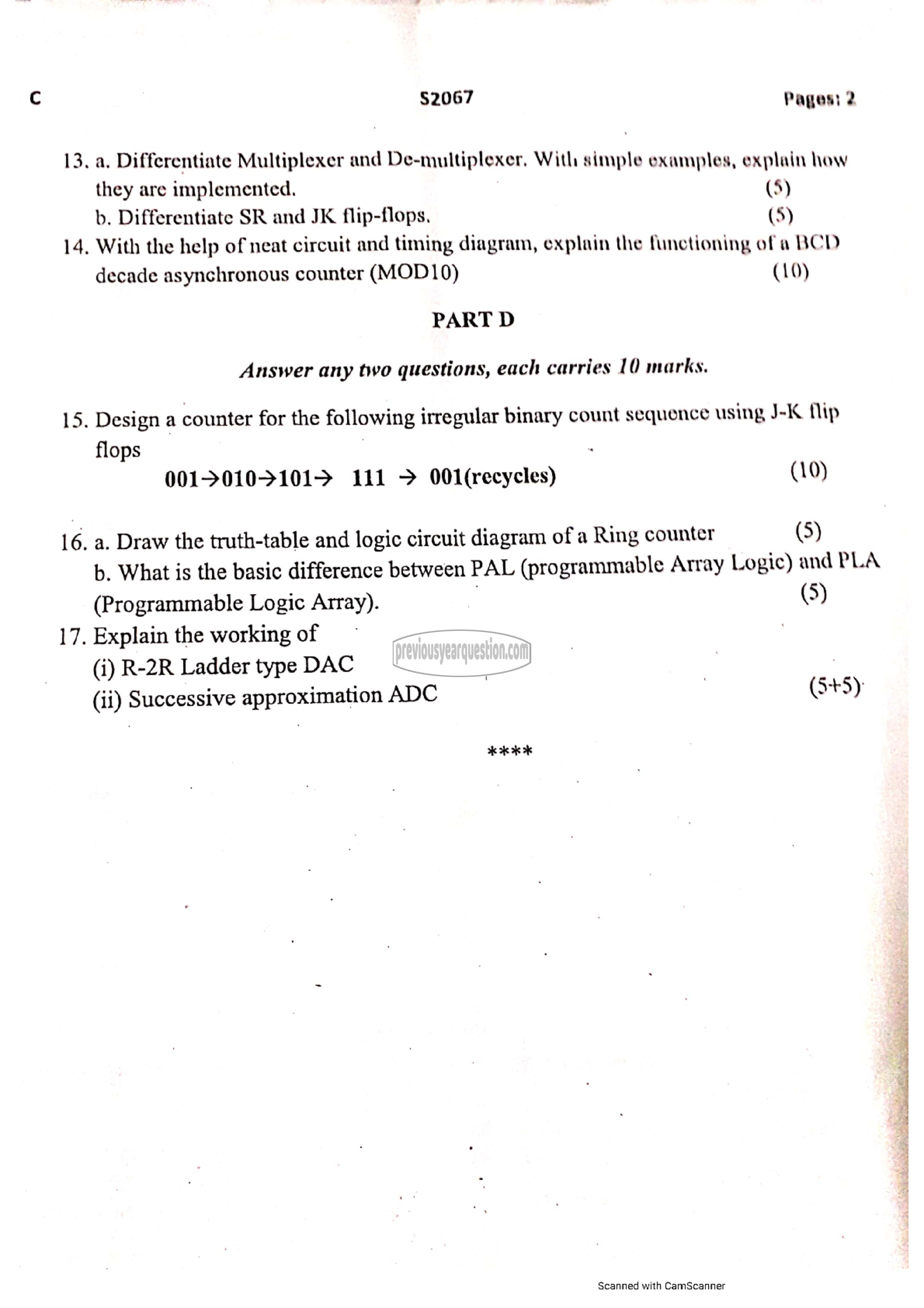

13. a. Differentiate Multiplexer and De-multiplexer, With simple examples, explain how

they are implemented. (5)

b. Differentiate SR and JK flip-flops, (5)

14. With the help of neat circuit and timing diagram, explain the functioning of a BCD

decade asynchronous counter (MOD10) (10)

PART D

Answer any two questions, each carries 10 marks.

15. Design a counter for the following irregular binary count sequence using 1-6 flip

flops

001501031015 111 > 001(recycles) (10)

16. a. Draw the truth-table and logic circuit diagram of a Ring counter (5)

b. What is the basic difference between PAL (programmable Array Logic) and PLA

(Programmable Logic Array). ۱ (5)

17. Explain the working of ⋅

(i) R-2R Ladder type DAC

(5+$)

(ii) Successive approximation ADC

AK عاد

Scanned with CamScanner

ಬೇ ಮು Shee Barc ಬ 211.3.